这是在ISE12.4上编译,链接到modelsim se6.5仿真的模块代码和测试代码。

//StateMachine.v version 1 状态机模块

module StateMachine(Clock, Reset, A, K2, K1, state);

input Clock, Reset, A;

output K2, K1;

output[1:0] state;

reg K2, K1;

reg[1:0] state;

parameter Idle = 2'b 00,

Start = 2'b 01,

Stop = 2'b 10,

Clear = 2'b 11;

always @(posedge Clock)

if(!Reset)

begin

state <= Idle;

K2 <= 0;

K1 <= 0;

end

else

case(state)

Idle:

if(A)

begin

state <= Start;

K1 <= 0;

end

else

begin

state <= Idle;

K2 <= 0;

K1 <= 0;

end

Start:

if(!A) state <= Stop;

else state <= Start;

Stop:

if(A)

begin

state <= Clear;

K2 <= 1;

end

else

begin

state <= Stop;

K2 <= 0;

K1 <= 0;

end

Clear:

if(!A)

begin

state <= Idle;

K2 <= 0;

K1 <= 0;

end

else

begin

state <= Clear;

K2 <= 0;

K1 <= 1;

end

default: state <= 2'b xx;

endcase

endmodule

//StateMachineTest.v测试代码

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 10:02:04 07/15/2011

// Design Name: z StateMachine

// Module Name: E:/FPGA Projects/ISE Projects/StateMachine/StateMachineTest.v

// Project Name: StateMachine

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: StateMachine

//

// Dependencies:

//

// Revision:*

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module StateMachineTest;

// Inputs

reg Clock;

reg Reset;

reg A;

// Outputs

wire K2;

wire K1;

wire [1:0] state;

// Instantiate the Unit Under Test (UUT)

StateMachine uut (

.Clock(Clock),

.Reset(Reset),

.A(A),

.K2(K2),

.K1(K1),

.state(state)

);

initial

begin

// Initialize Inputs

Clock = 0;

// Wait 100 ns for global reset to finish

forever #5 Clock = ~Clock;//产生驱动时钟

// Add stimulus here

end

initial

begin

A = 0;

forever #4 A = ~A;

end

initial

begin

Reset = 0;

#50

Reset = 1;

end

endmodule

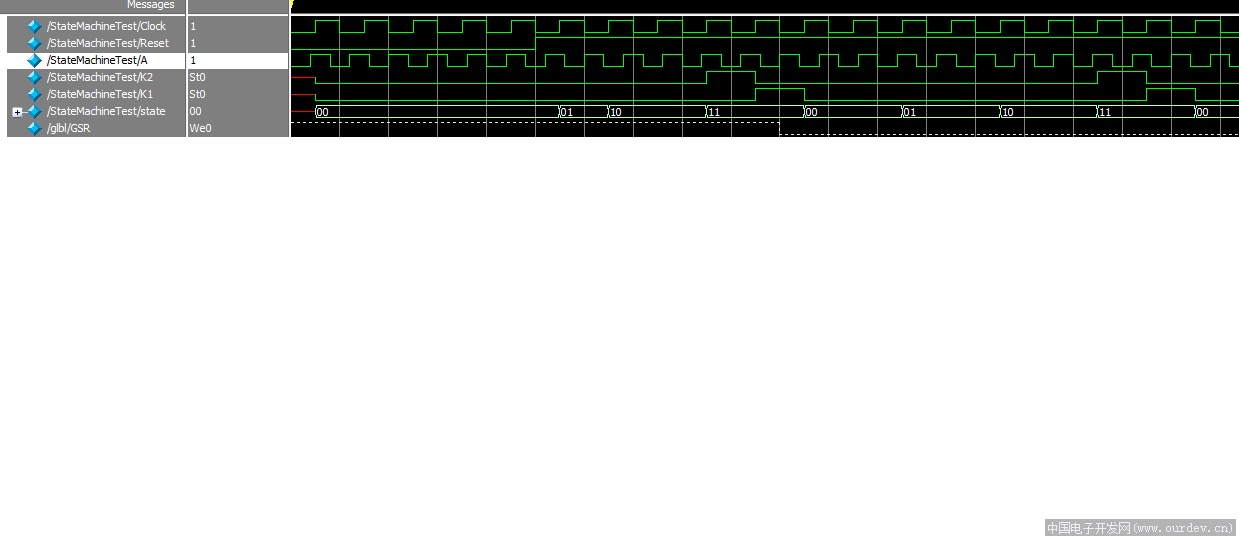

从波形上看,每一个状态所持续的时间是相等的。

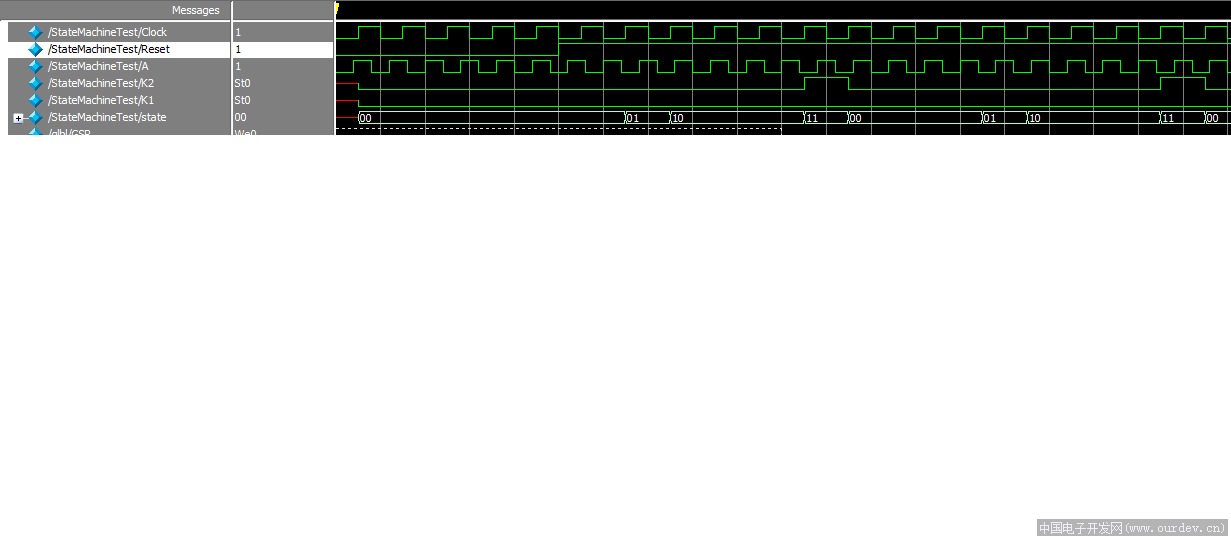

//StateMachine.v version 2 只是把case语句中的条件全部变成if(!A),而version1 的条件是一个if(A)下来一个if(!A)间隔出现。 同样的测试代码

module StateMachine(Clock, Reset, A, K2, K1, state);

input Clock, Reset, A;

output K2, K1;

output[1:0] state;

reg K2, K1;

reg[1:0] state;

parameter Idle = 2'b 00,

Start = 2'b 01,

Stop = 2'b 10,

Clear = 2'b 11;

always @(posedge Clock)

if(!Reset)

begin

state <= Idle;

K2 <= 0;

K1 <= 0;

end

else

case(state)

Idle:

if(!A)

begin

state <= Start;

K1 <= 0;

end

else

begin

state <= Idle;

K2 <= 0;

K1 <= 0;

end

Start:

if(!A) state <= Stop;

else state <= Start;

Stop:

if(!A)

begin

state <= Clear;

K2 <= 1;

end

else

begin

state <= Stop;

K2 <= 0;

K1 <= 0;

end

Clear:

if(!A)

begin

state <= Idle;

K2 <= 0;

K1 <= 0;

end

else

begin

state <= Clear;

K2 <= 0;

K1 <= 1;

end

default: state <= 2'b xx;

endcase

endmodule

version 1的测试代码的的仿真波形如下

version 1 仿真波形 (原文件名:StateMachineTestWaveV1.png)

version 2 仿真波形如下

version 2 仿真波形 (原文件名:StateMachineTestWaveV2.png)

产生这种仿真波形的原因是什么呢,这两种状态跳变条件的写法有什么不同,会对它的下一级产生追求者以影响 。 |

|

|

|