CPLD应用:增量式光栅旋转编码器的4倍频解码

刚学了几天的CPLD,上传我的第一个应用,不知道实际工作情况如何,希望高手指点指点,谢谢

如果CLK时钟频率为25Mhz,则至少可以对输出频率2.5Mhz以下增量式光栅旋转编码器的进行4倍频解码

概念如下:

增量式光栅旋转编码器分辨率:2500p/r (常用伺服系统的编码器)

按工作时最大的输出频率为2.5Mhz计算,编码器可以工作到60000r/m,当然这样的旋转速度实际上是很难达到的,实际上的常用的伺服电机最大工作到5000r/m

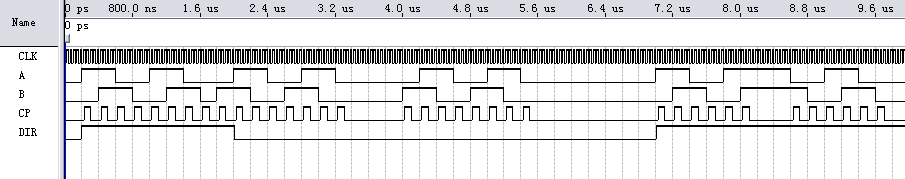

CLK:倍频用时钟频率

A:编码器A相

B:编码器B相

CP:解码后的脉冲

DIR:旋转方向

仿真图片如下:

Verilog hdl代码:

module decoder(CLK, A, B, CP, DIR);

input CLK;

input A;

input B;

output CP;

output DIR;

reg CP;

reg DIR;

wire a_xor_b;

reg a_xor_b_temp;

reg[3:0] a_xor_b_counter;

xor (a_xor_b, A, B);

always @(posedge CLK)

begin

if(a_xor_b_temp != a_xor_b)

begin

CP = 1'b1;

a_xor_b_temp = a_xor_b;

a_xor_b_counter = 4'b0000;

end

else

begin

a_xor_b_counter = a_xor_b_counter + 4'b0001;

if(a_xor_b_counter >= 4'b0010) // 根据实际应用,可以改变a_xor_b_counter上限值来改变输出脉宽

begin

CP = 1'b0;

end

end

end

always @(posedge A) begin

DIR = ~B;

end

endmodule |

|

|

|