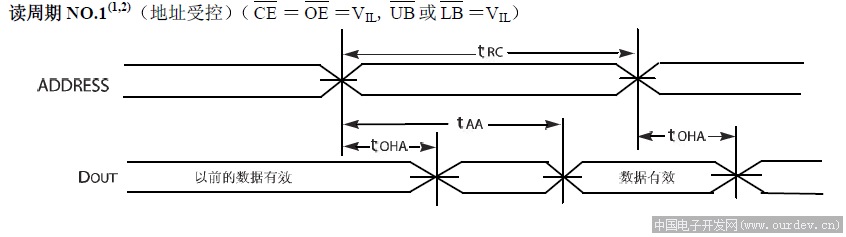

| 从网上载了几个SRAM控制代码,各种不能用。于是照着时序图写了一个,请各位看看有没有时序上的错误。 读时序  读时序 (原文件名:读时序.png) 写时序  写时序 (原文件名:写时序.png) oe、ce 接地, 用we信号控制读写, 我的操作过程如下: 读:1、打开读信号,锁存地址传到地址总线 2、锁存数据,关闭读信号 写:1、打开写信号,锁存地址和数据 2、等待SRAM总线高阻形成 3、关闭写信号,完成写过程 不知这样操作行不行? 代码如下: module sram_ctrl ( clk,rst_n, read,write,addr_i,wdata_i,rdata_o, SRAM_DQ, SRAM_ADDR,SRAM_LB_N,SRAM_UB_N,SRAM_CE_N,SRAM_OE_N,SRAM_WE_N ); input clk; input rst_n; input [22:0] addr_i; input read; input write; input [15:0] wdata_i; output [15:0] rdata_o; inout [15:0] SRAM_DQ; // SRAM Data bus 16 Bits output [22:0] SRAM_ADDR; // SRAM Address bus 18 Bits output SRAM_LB_N; // SRAM Low-byte Data Mask output SRAM_UB_N; // SRAM High-byte Data Mask output SRAM_CE_N; // SRAM Chip chipselect output SRAM_OE_N; // SRAM Output chipselect output SRAM_WE_N; // SRAM Write chipselect assign SRAM_LB_N=1'b1; assign SRAM_UB_N=1'b1; assign SRAM_OE_N=1'b1; assign SRAM_CE_N=1'b1; reg HIGHZ; reg [22:0] SRAM_ADDR_r; reg SRAM_WE_N_r; reg [15:0] rdata_r; reg [15:0] wdata_r; reg [2:0] CS; //状态寄存 parameter IDLE=0; parameter R_START=1; parameter R_FINISH=2; parameter W_START=3; parameter THIGHZ=4; parameter W_FINISH=5; always@(posedge clk or negedge rst_n) if(!rst_n)begin HIGHZ<=0; SRAM_WE_N_r<=1; SRAM_ADDR_r<=0; rdata_r<=0; wdata_r<=0; end else begin case(CS) IDLE: begin HIGHZ<=0; if(read) CS<=R_START; else if(write) CS<=W_START; else CS<=IDLE; end R_START:begin SRAM_WE_N_r<=1; SRAM_ADDR_r<=addr_i; CS<=R_FINISH; end R_FINISH:begin rdata_r<=SRAM_DQ; SRAM_WE_N_r<=0; CS<=IDLE; end W_START:begin SRAM_WE_N_r<=0; SRAM_ADDR_r<=addr_i; wdata_r<=wdata_i; CS<=THIGHZ; end THIGHZ:begin //等待SRAM总线上拉成高阻 CS<=W_FINISH; HIGHZ<=1; //高阻形成信号,送给inout做判断 end W_FINISH:begin SRAM_WE_N_r<=1; CS<=IDLE; end default:CS<=IDLE; endcase end assign SRAM_DQ=HIGHZ ? wdata_r : 16'bzzzz_zzzz_zzzz_zzzz; //HIGHZ控制inout方向 assign SRAM_WE_N=SRAM_WE_N_r; assign SRAM_ADDR=SRAM_ADDR_r; assign rdata_o=rdata_r; endmodule |